## Interface Control Document Between ALMA Phasing Project and ALMA Computing

## ALMA-05.11.00.00-70.35.25.00-A-ICD

2014-10-07

| Prepared By:    | Organization Role:       | Date and Signature: |

|-----------------|--------------------------|---------------------|

| R. Lacasse      | NRAO                     |                     |

| Geoff Crew      | Haystack Observatory     |                     |

| M. Honma        | NAOJ                     |                     |

| Approved By:    | Organization Role:       | Date and Signature: |

| Richard Lacasse | APP SE/Lead Engineer     |                     |

| Nick Whyborn    | ALMA Array Lead Engineer |                     |

| Jorge Ibsen     | ICT Manager              |                     |

| Released By:    | Organization Role:       | Date and Signature: |

| Michael Hecht   | APP Project Manager      |                     |

Interface Control Document Between ALMA Phasing Project And ALMA Computing Doc #: ALMA- 05.11.00.00-70.35.25.00-A-ICD Date: 2014-10-07 Status: Draft (*Draft, Pending, Approved, Released, Superseded, Obsolete*) Page: 2 of 44

### **Change Record**

| Version | Date                  | Affected<br>Section(s) | Change<br>Request # | Reason/Initiation/Remarks                                                                                                                                                                                                                                                                                         |

|---------|-----------------------|------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| А       | 2013-3-14             | ALL                    | None                | First Issue                                                                                                                                                                                                                                                                                                       |

| A01     | 2013-3-18             | Several                | None                | Incorporate comments by Geoff Crew and Alejandro<br>Saez                                                                                                                                                                                                                                                          |

| A02     | 2013-4-1              | Several                | None                | Change ANALOG_SUM_MODE protocol to use a 16-<br>msec sync instead of a 1-msec sync for PRN generator.<br>Add a requirement to the recorder's interface with<br>computing that it be able to connect to a server running<br>the NTP protocol.<br>Delete GET_VDIF_HEADER protocol<br>Update GET_PIC_STATUS protocol |

| A03     | 2013-4-15             | Several                | None                | Update per comments from Geoff Crew.                                                                                                                                                                                                                                                                              |

| A04     | 2013-4-22             | File name              | None                | Correct doc number in file name.<br>Update VDIF frame illustration (Fig. 3.6)                                                                                                                                                                                                                                     |

| A05     | 2013-5-11             | 3.1.1                  | None                | Correct reference to RD-01 (was RD-07)                                                                                                                                                                                                                                                                            |

| A06     | 2013-5-13             | Fig. 3-1               | None                | Correct outdated figure                                                                                                                                                                                                                                                                                           |

| A07     | 2013-8-9              | Doc. #                 | None                | Updated to current document number format                                                                                                                                                                                                                                                                         |

| A08     | 2013-8-19             | Several                | To Be Done          | Updated CAN-protocol-related numbers for LTA and SCC protocols.<br>Updated protocol description of both SCC commands.                                                                                                                                                                                             |

| A09     | 2013-8-22             |                        |                     | Fix typo on p. 20. PSN is 8 Bytes, not 4 Bytes.<br>Fix typo in 3.2.2.2.2. Changed<br>DOWNLOAD_VDIF_STATUS to<br>DOWNLOAD_VDIF_HEADER, 2 places                                                                                                                                                                    |

| A10     | 2014-2-28<br>2014-3-4 |                        |                     | Clarify the start-up procedure to show how the<br>commands must be synchronized to external timing.<br>This is included in the SET_PIC_CTRL protocol<br>description.<br>Change the statistics readout from 2 bytes to 3 bytes                                                                                     |

|         |                       |                        |                     | per state.<br>Add a bit in status word 52 to indicate whether the<br>ROACH is on or off.                                                                                                                                                                                                                          |

Interface Control Document Between ALMA Phasing Project And ALMA Computing Doc #: ALMA- 05.11.00.00-70.35.25.00-A-ICD Date: 2014-10-07 Status: Draft (*Draft, Pending, Approved, Released, Superseded, Obsolete*) Page: 3 of 44

| A11 | 2014-3-19 | - | - | Assign StructType to DOWNLOAD_VDIF_HEADER<br>and SET_PIC_CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|-----------|---|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |           |   |   | Assign function codes to APPLY_VDIF_HEADER,                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| A12 | 2014-4-2  | - | - | Add the time-to-completion of the<br>DOWNLOAD_VDIF_HEADER and<br>APPLY_VDIF_HEADER commands.<br>Changed title page:<br>prepared by: add Alejandro Saez<br>released by: replace Mark McKinnon with TBD                                                                                                                                                                                                                                                                                            |

| A13 |           |   |   | Specify zero as the structure type for<br>DOWNLOAD_VDIF_HEADER.<br>Specify 20503 as the Message RCA for<br>GET_DOWNLOAD_VDIF_HEADER_STATUS.<br>Specify the meaning of the bits in VDIFstatus for<br>protocol<br>GET_DOWNLOAD_VDIF_HEADER_STATUS.<br>Specify three as the function code for the<br>APPLY_VDIF_HEADER command.                                                                                                                                                                     |

| A14 | 2014-4-21 | - | - | GET_DOWNLOAD_VDIF_HEADER_STATUS:<br>Change RCA from 205xx to 20503. Specify values for<br>the return value.<br>APPLY_VDIF_HEADER: change function code from<br>x to 3.<br>GET_APPLY_VDIF_HEADER_STATUS: Change<br>RCA from 205xx and 20503 to 20504. Add several<br>possible states to the status<br>SET_PIC_CTRL: Change Type from X to 1. Clarify<br>the function of LDR, GRS, TGSD FMS and NVLD<br>control bits.<br>GET_PIC_STATUS: Change function code from X to<br>3 and type from Y to 0. |

| A15 | 2014-4-22 | - | - | Get_PIC_Status: Delete the "Type" parameterDOWNLOAD_VDIF_HEADER: Change the numberof bytes in data messages from 36 to 40.GET_DOWNLOAD_VDIF_HEADER_STATUS:clarify the possible values of the return value.                                                                                                                                                                                                                                                                                       |

| A16 | 2014-5-4  | - | - | Add applicable documents AD-06 and AD-07                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

Interface Control Document Between ALMA Phasing Project And ALMA Computing Doc #: ALMA- 05.11.00.00-70.35.25.00-A-ICD Date: 2014-10-07 Status: Draft (*Draft, Pending, Approved, Released, Superseded, Obsolete*) Page: 4 of 44

| A17 | 2014-5-4   | - | -                    | For the DOWNLOAD_VDIF_HEADER protocol,<br>change the "Data in Data Messages" from 36 to 40.<br>Clarify the startup procedure in SET_PIC_CTRL                                                                                                                                                                                                 |

|-----|------------|---|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A18 | 2014-5-6   | - | -                    | In the SET_PIC_CONTROL protocol,<br>• Change the definition of ICH<br>• Change the definition of SCH<br>In the GET_PIC_STATUS protocol, add bit 1 to the<br>ENV0 status byte                                                                                                                                                                 |

| A19 | 2014-5-15  | - | -                    | Update the DOWNLOAD_VDIF_HEADER protocol<br>to show what bits are sent by the CCC, and the<br>requirements for the least significant nibble of the<br>Magic Word.<br>Change the meaning of the bits in Word 5 to reflect<br>current status and future goals.                                                                                 |

| A20 | 2014-6-11  | - | -                    | Add a status bit to indicate FPGA write error to the protocol GET_APPLY_VDIF_HEADER_STATUS.                                                                                                                                                                                                                                                  |

| A21 | 2014-6-12  | - | -                    | Update Figure 3.6<br>Change the suggested startup procedure for the PIC<br>Clarify a typo concerning ROACH_write_error in<br>GET_APPLY_VDIF_STATUS<br>Add GrsFm to Control Byte 1                                                                                                                                                            |

| A22 | 2014-7-17  | - | -                    | Update GET_PIC_STATUS protocol to show the<br>availability of the sampled 1-PPS counter.<br>Modify figure 3-5 to show different binary codes for<br>data to Station Interface Card and Phasing Interface<br>Card.                                                                                                                            |

| A23 | 2014-8-1   | - | -                    | Update DOWNLOAD_VDIF_HEADER protocol to<br>show details of the status words provided by the PIC in<br>the VDIF data frames<br>Incorporate Geoff's comments to the draft of the<br>above.<br>Change the recommended PIC startup procedure (step<br>4d).<br>In the CAN protocol GET_PIC_Status, added bits 2, 3<br>and 4 to PIC status byte 53 |

| A24 | 2014-9-10  | - | -                    | In SET_PIC_CONTROL, add bit 2 in control word 1 to enable re-seeding of the PRN test data generator                                                                                                                                                                                                                                          |

| A25 | 2014-09-10 |   | Alejandro<br>Caceres | Regular ICD number assigned                                                                                                                                                                                                                                                                                                                  |

Interface Control Document Between ALMA Phasing Project And ALMA Computing Doc #: ALMA- 05.11.00.00-70.35.25.00-A-ICD Date: 2014-10-07 Status: Draft (*Draft, Pending, Approved, Released, Superseded, Obsolete*) Page: 5 of 44

| A26 | 2014-09-29 | F.<br>Sepulveda | Signature matrix modified according to N. Whyborn's comments.                                                                                                                                                              |

|-----|------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A27 | 2014-10-07 | R. Lacasse      | <ul> <li>Respond to Nick Whyborn's comments:</li> <li>TBDs removed</li> <li>Added applicable docs to provide req. info</li> <li>Clarified responsibility for recorder interface.</li> <li>Fix a typo in Table 3</li> </ul> |

Interface Control Document Between ALMA Phasing Project And ALMA Computing Doc #: ALMA- 05.11.00.00-70.35.25.00-A-ICD Date: 2014-10-07 Status: Draft (*Draft, Pending, Approved, Released, Superseded, Obsolete*) Page: 6 of 44

#### **Table of Contents**

| 1 <b>E</b> | Description                                                        | 8 |

|------------|--------------------------------------------------------------------|---|

| 1.1        |                                                                    |   |

| 1.2        | Scope                                                              | 8 |

| 2 A        | Applicable Document, Reference Documents, Acronyms and Definitions | 8 |

| 2.1        | Applicable Documents                                               | 8 |

| 2.2        | Reference Documents                                                | 9 |

| 2.3        | Abbreviations and Acronyms                                         | 9 |

| 2.4        | Definitions1                                                       | 1 |

| 3 I        | nterfaces to Various Subsystems1                                   |   |

| 3.1        | Hydrogen Maser1                                                    | 1 |

|            | 3.1.1 Introduction                                                 | 1 |

|            | 3.1.2 Background                                                   | 1 |

|            | 3.1.1 H-Maser Interface to Computing                               | 3 |

| 3.2        | 2 64-Antenna Correlator Upgrades1                                  | 3 |

|            | 3.2.1 Introduction                                                 | 4 |

|            | 3.2.2 Interface to Computing                                       |   |

|            | 3.2.3 Other Interfaces to PIC                                      | 1 |

| 3.3        | Optical Fiber Link System Interface                                | 2 |

|            | 3.3.1 Interface to Computing                                       | 2 |

| 3.4        | VLBI Recorder Interface                                            | 2 |

|            | 3.4.1 Subsystem Description                                        | 2 |

|            | 3.4.2 Interface to Computing                                       | 3 |

Interface Control Document Between ALMA Phasing Project And ALMA Computing Doc #: ALMA- 05.11.00.00-70.35.25.00-A-ICD Date: 2014-10-07 Status: Draft (*Draft, Pending, Approved, Released, Superseded, Obsolete*) Page: 7 of 44

#### **List of Figures**

| Figure 3-1  | - ALMA CLOA (shaded red box), with interface to Correlator and Antennas             |    |

|-------------|-------------------------------------------------------------------------------------|----|

| indica      | ted. Before ALMA Phasing Project elements are added.                                | 12 |

| Figure 3-2  | - ALMA CLOA (shaded red box), with interface to Correlator and Antennas             |    |

| indica      | ted, with ALMA Phasing Project elements added                                       | 13 |

| Figure 3-3. | Block diagram showing the scaling of the sum and routing of 2-bit results to the Pl | IC |

| and CI      |                                                                                     | 18 |

| Figure 3-4. | Sketch showing the mapping of the mask bits                                         | 18 |

| Figure 3-5. | Illustration of the effect of the threshold to the mapping of memory addresses      |    |

| (corres     | sponds to sums) to memory outputs (corresponds to scaled sum)                       | 20 |

| Figure 3-6. | VDIF frame format for the PIC                                                       | 26 |

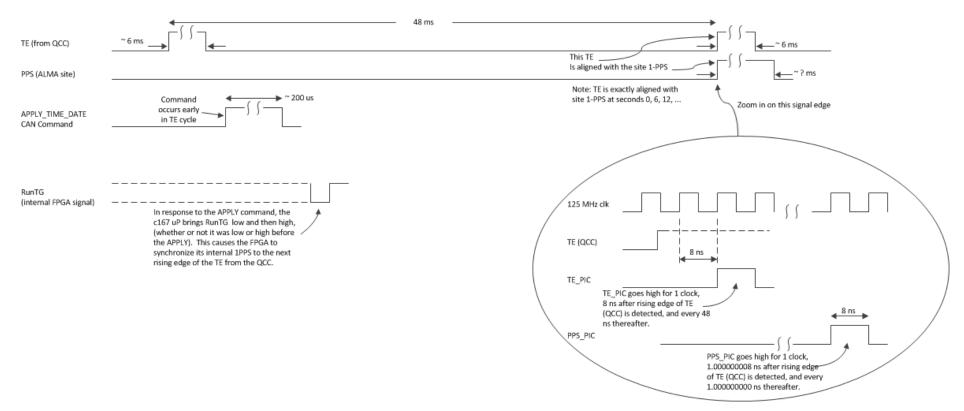

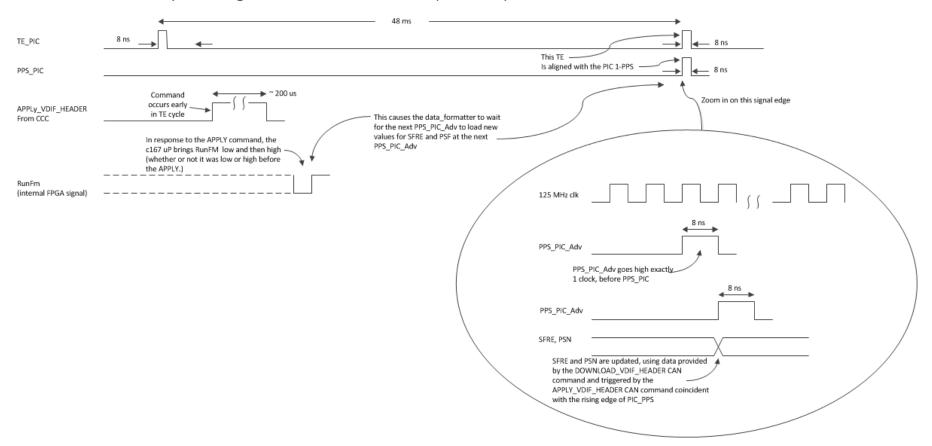

| Figure 3-7. | Timing diagram which provides details in synchronizing the internal 1PPS to the     |    |

| externa     | al timing reference                                                                 | 35 |

| Figure 3-8. | Timing diagram which provides details in synchronizing "seconds from reference      |    |

| epoch'      | ' and "packet serial number" to the internal timing references                      | 36 |

| Figure 3-9. | Photo of one of four recorders required for the APP.                                | 43 |

Interface Control Document Between ALMA Phasing Project And ALMA Computing Doc #: ALMA- 05.11.00.00-70.35.25.00-A-ICD Date: 2014-10-07 Status: Draft (*Draft, Pending, Approved, Released, Superseded, Obsolete*) Page: 8 of 44

### 1 **Description**

#### 1.1 Purpose

This ICD covers the all interfaces between ALMA Computing and the ALMA Phasing Project (APP) equipment.

#### 1.2 Scope

The ALMA Phasing Project provides ALMA with the capability of phasing up to 63 Antennas and recording the resulting data for later correlation at another facility (e.g., Haystack Observatory). Equipment associated with the project includes a hydrogen maser for VLBI phase stability, various upgrades to the 64-Antenna Correlator, an optical data transmission system to transmit data over a single fiber from the AOS to OSF and a data recording system. This equipment is more fully described elsewhere [**AD-01**]. Some of these subsystems may have several interfaces to the ALMA Observatory (e.g. hardware and software). This document covers only the interfaces between new APP equipment and Computing. Software-to-software interfaces are covered in design documents [**AD-02**, **RD-06**]. Access to the new hardware in normal operations is made via the VLBI Observing Mode (VOM) and is documented in its design document [**AD-02**].

The ALMA Phasing Project is identified in the following document: [AD 01].

### 2 Applicable Document, Reference Documents, Acronyms and Definitions

Applicable documents are necessary for the understanding of this document. In some cases, they provide additional requirements which are to be incorporated into the ICD. Reference documents are supplemental and simply provide further reference for various topics. In most cases, the acronyms used in this document are consistent with ALMA defined acronyms, however additional acronyms have also been listed which are outside the scope of ALMA definitions. No distinction is made between these two uses.

#### **2.1 Applicable Documents**

The following documents, of the exact issue shown, form part of this document. In the event of conflict between the documents listed here and this document, this document shall take precedence.

Interface Control Document Between ALMA Phasing Project And ALMA Computing Doc #: ALMA- 05.11.00.00-70.35.25.00-A-ICD Date: 2014-10-07 Status: Draft (*Draft, Pending, Approved, Released, Superseded, Obsolete*) Page: 9 of 44

| Number  | Document Title                                          | Reference                                            |

|---------|---------------------------------------------------------|------------------------------------------------------|

| [AD 01] | APP Project Plan Release 1.3                            | ALMA Phasing Project, Project Plan 1.3,<br>11-Oct-12 |

| [AD 02] | ALMA Phasing Project Update to Corr/Control Design      | ALMA-05.11.61.01-001-A-DSN                           |

| [AD 03] | ALMA Environmental Specification                        | ALMA-80.05.02.00-001-B-SPE                           |

| [AD 04] | Seismic Design Specifications for ALMA-AOS and ALMA-OSF | SYSE-80.10.00.00-002-B-REP                           |

| [AD 05] | Latest Prod. Assurance Requirements                     | ALMA-05.11.10.01.0002-A-PLA                          |

| [AD 06] | APP Update to Corr/Control Design                       | ALMA-05.11.61.01-001-A-DSN                           |

| [AD 07] | APP Update to TelCal Design                             | ALMA-05.11.62.01-001-A-DSN                           |

| [AD 08] | XW-100_protocol_rev2                                    |                                                      |

| [AD 09] | Mark6_command_set-Release1.1                            |                                                      |

#### Table 2-1. Applicable Documents for this ICD

#### **2.2 Reference Documents**

| Number  | Document Title                                                                                             | Reference                                                                             |

|---------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

|         |                                                                                                            |                                                                                       |

| [RD 01] | iMaser <sup>™</sup> 3000, Installation, Operation &<br>Maintenance User Manual, Issue 1.7, 28-<br>May-2010 | T4S-MAN-0012, available from www.T4Science.com                                        |

| [RD 02] | iMaser <sup>™</sup> 3000 Specifications                                                                    | http://www.t4science.com/documents/iMaser_Clock_<br>Spec.pdf                          |

| [RD 03] | 64 Antenna Correlator<br>Specifications and Requirements                                                   | ALMA-60.00.00.00-001-B-SPE                                                            |

| [RD 04] | Interface Control Document Between 64-<br>Antenna Correlator And Correlator<br>Computing System            | ALMA-60.00.00.00-70.40.00.00-D-ICD                                                    |

| [RD 05] | VLBI Data Interchange Format (VDIF)<br>Specification                                                       | http://www.vlbi.org/vdif/docs/VDIF%20specification<br>%20Release%201.0%20ratified.pdf |

| [RD 06] | APP Update to TelCal Design                                                                                | ALMA-05.11.62.01-001-A-DSN                                                            |

| [RD-07] | Interface Control Document between ALMA<br>Phasing Project and ALMA Correlator                             | ALMA-05.11.10.49-60.00.00.00-A-ICD                                                    |

Table 2-2. Reference Documents for this ICD

#### 2.3 Abbreviations and Acronyms

| AC | Alternating Current |

|----|---------------------|

| AD | Applicable Document |

Interface Control Document Between ALMA Phasing Project And ALMA Computing Doc #: ALMA- 05.11.00.00-70.35.25.00-A-ICD Date: 2014-10-07 Status: Draft (*Draft, Pending, Approved, Released, Superseded, Obsolete*) Page: 10 of 44

| ALMAAtacama Large Millimeter Array radio telescopeAOSArray Operations Site           |      |

|--------------------------------------------------------------------------------------|------|

| AUS   Array Operations Sile                                                          |      |

|                                                                                      |      |

| APP ALMA Phasing Project                                                             |      |

| ATX Advanced Technology eXtended (standard for Personal Computers)                   |      |

| BE Back End                                                                          |      |

| CLOA Central LO Article                                                              |      |

| CAI Correlator Antenna Input                                                         |      |

| CIC Correlator Interface Card                                                        |      |

| CRG Central Reference Generator LRU                                                  |      |

| CVR Central Variable Reference LRU                                                   |      |

| CVRR         Central Variable Reference Rack                                         |      |

| DLO Digital Local Oscillator                                                         |      |

| GPS Global Positioning Service                                                       |      |

| HMR Hydrogen Maser Rack                                                              |      |

| ICD Interface Control Document                                                       |      |

| IPT Integrated Product Team                                                          |      |

| LLCR Line Length Corrector Rack                                                      |      |

| LO Local Oscillator                                                                  |      |

| LRU Line Replaceable Unit                                                            |      |

| LVDS Low Voltage Differential Signal                                                 |      |

| M&C Monitor and Control                                                              |      |

| MFS Master Frequency Standard LRU                                                    |      |

| ML Master Laser LRU                                                                  |      |

| NRAO National Radio Astronomy Observatory                                            |      |

| PAI Preliminary Acceptance In-House                                                  |      |

| PAS Provisional Acceptance On-Site                                                   |      |

| PDU Power Distribution Unit                                                          |      |

| PIC Phasing Interface Card                                                           |      |

| PLOTS Photonic LO Test Stand                                                         |      |

| PPS Pulse Per Second                                                                 |      |

| PRDR         Photonic Reference Distribution Rack                                    |      |

| PRR Photonic Reference Rack                                                          |      |

| RF Radio Frequency                                                                   |      |

| RFI   Radio Frequency Interference                                                   |      |

| SASR Sub Array Switch Rack                                                           |      |

| <b>TE</b> Timing Event (a 48-msec timing tick which is the heartbeat of the ALMA con | trol |

| system)                                                                              |      |

| TSM Temperature Sensor Module                                                        |      |

**Interface Control Document Between ALMA Phasing Project** And ALMA Computing

Doc #: ALMA- 05.11.00.00-70.35.25.00-A-ICD Date: 2014-10-07 Status: Draft (Draft, Pending, Approved, Released, Superseded, Obsolete) 11 of 44 Page:

| UPS  | Uninterruptable Power Supply      |

|------|-----------------------------------|

| VDIF | VLBI Data Interchange Format      |

| VEX  | VLBI EXperiment                   |

| VLBI | Very Long Baseline Interferometry |

#### 2.4 Definitions

None so far...

### **3** Interfaces to Various Subsystems

This section includes the detailed interfaces to the various subsystems comprising the ALMA Phasing System. A section is dedicated to each subsystem.

#### 3.1 Hydrogen Maser

#### 3.1.1 Introduction

VLBI observations require extremely good phase stability because the phase stability between geographically separated telescopes is required (Allan deviation of 2 e-15 at 1000 seconds). This is a contrast with connected interferometers, like ALMA, where frequency references for all antennas are derived from a single reference. The frequency reference provided with the original ALMA array, a rubidium standard, while adequate for connected-element interferometry, is not adequate for VLBI at millimeter wavelengths. Thus a hydrogen maser is provided as a deliverable of the Phasing Project.

In particular, the hydrogen maser provided is:

Manufacturer: T4 Science SA Model Number: iMaser 3000

The interfaces of this subsystem to computing are detailed in this section.

#### 3.1.2 Background

The ALMA Central Local Oscillator was installed in 2009, and expanded in 2011. It has been in use since that time for ALMA Early Science. The ALMA Phasing Project (APP) is an external

international development effort that will enable ALMA to participate in ultra-high resolution VLBI and high frequency phased array science [AD 01].

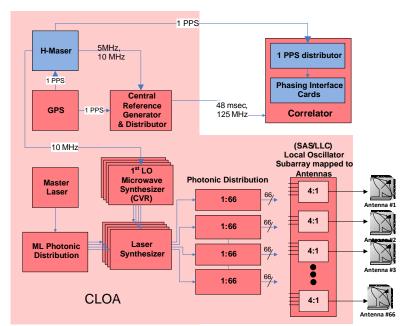

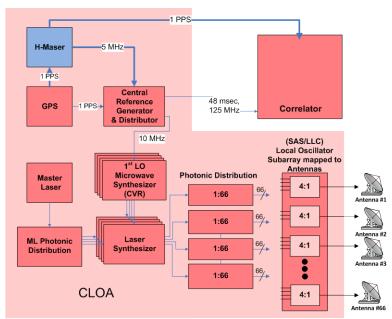

The following block diagram illustrates the interface that is the subject of this document. This diagram is consistent with Figure 2.1 of [AD 01] but adds detail to the CLOA elements: H-Maser, GPS, CRD, CRG, CVR, ...etc.

In the first figure, the ALMA CLOA is shown before the addition of elements required for the ALMA Phasing Project.

Figure 3-1 - ALMA CLOA (shaded red box), with interface to Correlator and Antennas indicated. Before ALMA Phasing Project elements are added.

The changes necessary to accommodate the ALMA Phasing Project are shown next.

Interface Control Document Between ALMA Phasing Project And ALMA Computing Doc #: ALMA- 05.11.00.00-70.35.25.00-A-ICD Date: 2014-10-07 Status: Draft (*Draft, Pending, Approved, Released, Superseded, Obsolete*) Page: 13 of 44

# Figure 3-2 - ALMA CLOA (shaded red box), with interface to Correlator and Antennas indicated, with ALMA Phasing Project elements added.

The added elements are the following:

- Hydrogen Maser (H-Maser)

- H-Maser Rack (HMR)

- Change of 1 PPS from MFS to H-Maser

- Change of 5 MHz now coming from the H-Maser to the MFS

- Addition of 1 PPS from H-Maser to Correlator (CORR)

#### 3.1.1 H-Maser Interface to Computing

The maser includes a software interface which is documented in **[RD 01]**. To monitor the health of the maser, the ALMA Monitor and Control System shall use this interface to monitor and log the parameters listed in Table 2 of this manual. This interface is fully described in **[AD-02]**.

#### 3.2 64-Antenna Correlator Upgrades

**Interface Control Document Between ALMA Phasing Project**  Doc #: ALMA- 05.11.00.00-70.35.25.00-A-ICD Date: 2014-10-07 Status: Draft (Draft, Pending, Approved, Released, Superseded, Obsolete) 14 of 44 Page:

#### 3.2.1 Introduction

The specification for the 64-Antenna Correlator [RD 10] includes a requirement that the correlator provide "hooks" for VLBI. To take advantage of these hooks, various modifications to the correlator are required. Hardware modifications to the correlator are documented separately in [RD-07]. This section details the new CAN protocols required to implement the APP. Existing Correlator CAN protocols are documented in [RD 04].

#### 3.2.2 Interface to Computing

**[RD 04]** includes a section (section 16 in version D) describing the interface between the "Correlator and Computing Correlator System". The introductory part of this section provides a general overview of the CAN interface between computing and correlator. This is not repeated here. Also, certain *existing* CAN protocols, which are indispensable to implementing the phasing interface, are not repeated here. The following sections describe only new capabilities required for implementing phasing. Recall that a new type of card, the PIC, is added to the correlator. Two such cards are required per quadrant. The PIC card shall also respond to all "Protocols That Apply to All types of Nodes" (section 16.3 in [RD 11]).

#### 3.2.2.1 **Protocols Specific to LTA Nodes**

Since the actual summing of signals from antennas takes place in the correlator cards, which are controlled by the LTAs, some new protocols are required to control and monitor this functionality. A short summary of the new protocols required includes:

- Provide a mask to specify which antennas are summed

- Provide the capability to substitute test data for normal data in the sum

- Provide the capability to control a switch which in turns provides the capability to inject the sum into the correlator matrix in place of the 64<sup>th</sup> antenna.

- Provide data for mapping the sum from 8 bits to 2 bits.

- Provide a means of monitoring the status of the above commands

#### 3.2.2.1.1 **DOWNLOAD ANTENNA SUM MASK: Function Code** 2, Type 11

Type: **Description**: Typical Interval: Broadcast, Data\_msg\_ID = 8, Func code 2, Structure type 11 Provides a mask to select which antennas to sum Before the start of data taking

Data[6]

Data[7]

**Interface Control Document Between ALMA Phasing Project** And ALMA Computing

Doc #: ALMA- 05.11.00.00-70.35.25.00-A-ICD Date: 2014-10-07 Status: Draft (Draft, Pending, Approved, Released, Superseded, Obsolete) 15 of 44 Page:

Mask Byte 7

Data in Data Messages: 2 bytes

Target mask

Target mask

39 - 32

47 - 40

|         | Fixed length message pay | vloads = 8 bytes            | 8 bytes           |  |

|---------|--------------------------|-----------------------------|-------------------|--|

| Message | Broadcast Setup          | Header                      | First & Only Data |  |

| Payload | Message                  | Message                     | Message           |  |

| Bytes   |                          |                             |                   |  |

|         | Transmit using           | Transmit using              | Transmit using    |  |

|         | Message ID 5             | Message ID 8                | Message ID 9      |  |

|         |                          |                             |                   |  |

| Data[0] | $Data_msg_ID = 8$        | Func_code=2                 | Mask Byte 0       |  |

| Data[1] | 0 (spare)                | Struct_type 11              |                   |  |

| Data[2] | Target mask 7 - 0        | LS block size (bytes) $= 8$ |                   |  |

| Data[3] | Target mask 15 - 8       | MS block size (bytes) $= 0$ |                   |  |

| Data[4] | Target mask 23 - 16      | 0 (spare)                   |                   |  |

| Data[5] | Target mask 31 - 24      | 0 (spare)                   |                   |  |

0 (spare)

0 (spare)

Byte 0 is the LS byte, corresponding to CAIs 7 down to 0, and so forth up through Byte 7 for CAIs 63 down to 56. A one in a bit position specifies that the CAI is included in the sum. A zero specifies that it is not. Bit 7 of byte 7 should always be zero since this antenna input is used by the phasing system to input the sum into the correlator matrix. A 1 in this bit position will be flagged as a warning in the status message. A zero in this position will always be downloaded to hardware and returned as status by the firmware in the LTA.

This command does not require an "apply". The mask is changed right after the command is received.

#### SET\_ANALOG\_SUM\_MODE: Function Code 11 3.2.2.1.2

Broadcast,  $Data_msg_ID = 8$ , Func code 11 Type: Description: Used to select between normal and test data Typical Interval: Before the start of data taking Data in Data Messages: 2 bytes

This protocol directs the analog sum logic to provide either normal data or one of four possible test data streams.

Interface Control Document **Between ALMA Phasing Project** And ALMA Computing

Doc #: ALMA- 05.11.00.00-70.35.25.00-A-ICD Date: 2014-10-07 Status: Draft (Draft, Pending, Approved, Released, Superseded, Obsolete) Page: 16 of 44

|         | Fixed length message payloads $= 8$ bytes |                                    |  |

|---------|-------------------------------------------|------------------------------------|--|

| Message | Broadcast Setup                           | Header                             |  |

| Payload | Message                                   | Message                            |  |

| Bytes   | Transmit using                            | Transmit using                     |  |

| -       | Message ID 5                              | Message ID 8                       |  |

| Data[0] | Data_msg_ID = 8                           | Func_code=11                       |  |

| Data[1] | 0 (spare)                                 | MODE 0-4 (selects sum output type) |  |

| Data[2] | Target mask 7 - 0                         | 0 (spare)                          |  |

| Data[3] | Target mask 15 - 8                        | 0 (spare)                          |  |

| Data[4] | Target mask 23 - 16                       | 0 (spare)                          |  |

| Data[5] | Target mask 31 - 24                       | 0 (spare)                          |  |

| Data[6] | Target mask 39 - 32                       | 0 (spare)                          |  |

| Data[7] | Target mask 47 - 40                       | 0 (spare)                          |  |

The following table identifies the input source selection options:

| Data[1] | Sum Output Type                   |

|---------|-----------------------------------|

| 0       | Antenna Sum (normal data)         |

| 1       | Static logic level 0              |

| 2       | Pseudo random data, sync'd to 16  |

|         | msec tic                          |

| 3       | Pseudo random data, not sync'd to |

|         | tic                               |

| 4       | Binary counter                    |

This type of flexibility on output data is similar to that provided in other parts of the correlator. It has proven useful in measuring the reliability of the links between subsystems as well as aiding with troubleshooting. In this instance, it will make it possible to evaluate the reliability of the link to the PIC cards and downstream link.

This command does not require an "apply". The switch is changed right after the command is received.

#### 3.2.2.1.3 SET\_CIC\_SUM\_INPUT\_SWITCH

Type: Description: Typical Interval: Data in Data Messages:

Broadcast, Data\_msg\_ID = 8, Func code 12 Provides a bit to set the state of the CIC input switch Before the start of data taking 2 bytes

There is an electronic switch in the Correlator Interface Cards, which allows for selection of two possible inputs for the 64<sup>th</sup> antenna, CAI 63. The first is the normal data from CAI 63. The second is the phased sum data from the correlator card. The hardware default, after a system reset, is normal data, so that this protocol needs to be used only in phasing mode.

|         | Fixed length message payloads = 8 bytes |                                                                   |  |  |  |

|---------|-----------------------------------------|-------------------------------------------------------------------|--|--|--|

| Message | Broadcast Setup                         | Header                                                            |  |  |  |

| Payload | Message                                 | Message                                                           |  |  |  |

| Bytes   | Transmit using                          | Transmit using                                                    |  |  |  |

| -       | Message ID 5                            | Message ID 8                                                      |  |  |  |

| Data[0] | Data_msg_ID = 8                         | Func_code=12                                                      |  |  |  |

| Data[1] | 0 (spare)                               | Switch Position Bit ( $0 = normal data$ ; $1 = phased sum data$ ) |  |  |  |

| Data[2] | Target mask 7 - 0                       | 0 (spare)                                                         |  |  |  |

| Data[3] | Target mask 15 - 8                      | 0 (spare)                                                         |  |  |  |

| Data[4] | Target mask 23 - 16                     | 0 (spare)                                                         |  |  |  |

| Data[5] | Target mask 31 - 24                     | 0 (spare)                                                         |  |  |  |

| Data[6] | Target mask 39 - 32                     | 0 (spare)                                                         |  |  |  |

| Data[7] | Target mask 47 - 40                     | 0 (spare)                                                         |  |  |  |

This command does not require an "apply". The switch is changed right after the command is received.

#### 3.2.2.1.4 DOWNLOAD\_SUM\_SCALING\_DATA

Summing the 2-bit data from the ALMA antennas in the observing Array will result in a sum which has at most 256 possible values. To be fed back to the correlator or delivered to the PIC, this sum must be again reduced to a 2-bit quantity with proper statistics (i.e. one of 4 states representing -3, -1, +1 or +3, with Gaussian distribution).

The mapping of 256 to 4 values is a function of the number of antennas N and can be provided to the LTA logic equivalently as a lookup table or as the 3 thresholds dividing the 4 output states, and the limiting valid values. Even more simply, one can assume zero offset and provide a single number, the positive threshold and assume the negative threshold is symmetrical. Initially, we plan to implement the simplest choice. Details for this choice are presented in Section 3.2.2.1.4.2.

#### 3.2.2.1.4.1 Background information

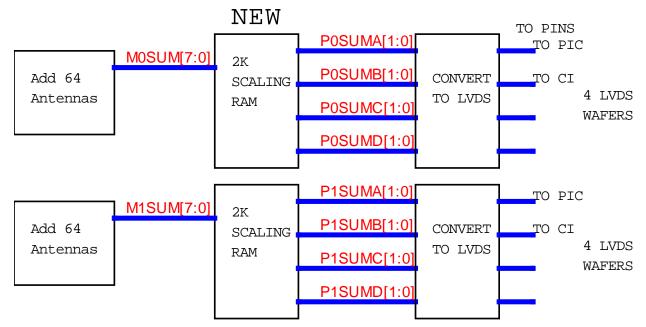

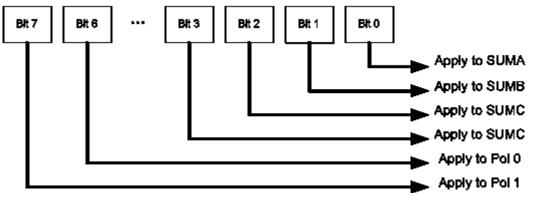

The summing hardware is capable of providing 4 sets (A through D) of two bit numbers for each of two polarizations (P0 and P1) as shown in Figure 3-3 below. We expect that, for our application, all four sets will be identical. The capability of making them different is provided,

however, since is it fairly simple to do so. The protocol to deliver the 8- to 2-bit mapping information thus is applicable to one or more configurations as specified by a **mask** variable in the headers. The interpretation of the mask bits is as shown in Figure 3-4 below.

Figure 3-3. Block diagram showing the scaling of the sum and routing of 2-bit results to the PIC and CI.

Figure 3-4. Sketch showing the mapping of the mask bits.

NB: There is no basis at present for thinking we need a separate map for the A and B channels (i.e. the PIC should produce exactly what is fed back to the correlator), or for a separate map for

Interface Control Document Between ALMA Phasing Project And ALMA Computing Doc #: ALMA- 05.11.00.00-70.35.25.00-A-ICD Date: 2014-10-07 Status: Draft (*Draft, Pending, Approved, Released, Superseded, Obsolete*) Page: 19 of 44

P0 and P1 (the polarization sums should be handled identically). Since C and D are not connected, the mask would then always be 0xC3.

#### 3.2.2.1.4.2 Message with one threshold

| Type:                  | Broadcast, Data_msg_ID = 8, Func code 13                     |

|------------------------|--------------------------------------------------------------|

| Description:           | Provides threshold and mask for mapping 8-bit data to 2 bits |

| Typical Interval:      | Before the start of data taking                              |

| Data in Data Messages: | 3 bytes                                                      |

The protocol we have selected to implement uses one threshold. It is described in this section.

| Message | Broadcast Setup     | Header         |

|---------|---------------------|----------------|

| Payload | Message             | Message        |

| Bytes   | Transmit using      | Transmit using |

|         | Message ID 5        | Message ID 8   |

| Data[0] | Data_msg_ID = 8     | Func_code=13   |

| Data[1] | 0 (spare)           | Mask           |

| Data[2] | Target mask 7 - 0   | pos2high_th    |

| Data[3] | Target mask 15 - 8  | 0 (spare)      |

| Data[4] | Target mask 23 - 16 | 0 (spare)      |

| Data[5] | Target mask 31 - 24 | 0 (spare)      |

| Data[6] | Target mask 39 - 32 | 0 (spare)      |

| Data[7] | Target mask 47 - 40 | 0 (spare)      |

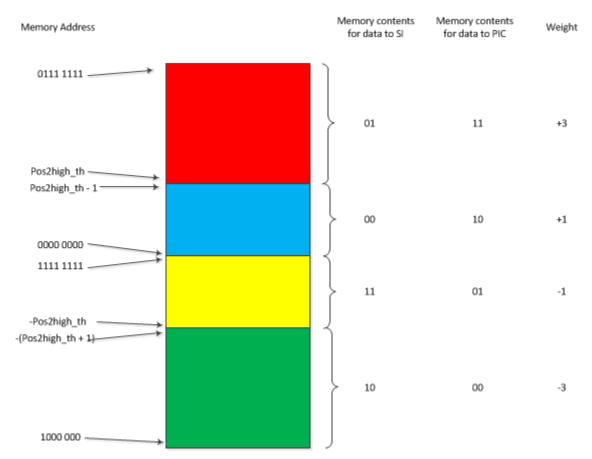

mask:controls applicability as defined above (Figure 3-4)pos2high\_th:the positive threshold. See figure below for details. At and above this<br/>threshold, the memory output shall be 01 for data to the Station Interface<br/>Card (SI) and 11 for data to the PIC.

Figure 3-5. Illustration of the effect of the threshold to the mapping of memory addresses (corresponds to sums) to memory outputs (corresponds to scaled sum)

This command does not require an "apply". The switch is changed right after the command is received.

#### 3.2.2.1.1 GET\_SUM\_STATUS

| RCA                      | 0x1000, FC 14                                                          |

|--------------------------|------------------------------------------------------------------------|

| Description              | Returns status information from all of the above commands              |

| Typical Interval<br>Data | After executing above commands<br>8 bytes<br>GET: returns status info. |

Interface Control Document Between ALMA Phasing Project And ALMA Computing Doc #: ALMA- 05.11.00.00-70.35.25.00-A-ICD Date: 2014-10-07 Status: Draft (*Draft, Pending, Approved, Released, Superseded, Obsolete*) Page: 21 of 44

| Message<br>Payload<br>Bytes | Control Message<br>(identical for both the<br>request and response ) | Data<br>Messages<br>(All but last) | ••• | Last Data Message<br>Message RCA |

|-----------------------------|----------------------------------------------------------------------|------------------------------------|-----|----------------------------------|

|                             | Message RCA<br>0x1000                                                | Message RCA<br>0x1000              |     | 0x1001                           |

| Data[0] | Func_code=14           | Mask Byte 0 | MODE 0-4        |

|---------|------------------------|-------------|-----------------|

| Data[1] | 0 (spare)              |             | Switch Position |

| Data[2] | LS struct size (bytes) |             | Mapping Mask    |

| Data[3] | MS struct size (bytes) |             | pos2high_th     |

| Data[4] | 0 (spare)              |             | -pos2high_th    |

| Data[5] | 0 (spare)              |             | spare           |

| Data[6] | 0 (spare)              |             | spare           |

| Data[7] | 0 (spare)              | Mask Byte 7 | spare           |

**Description of data in the message:**

Mask Byte 0 to 7: The mask transmitted by the previous DOWNLOAD\_ANTENNA\_SUM\_MASK command.

**Switch Position:** The switch position transmitted by the previous SET\_CIC\_SUM\_INPUT SWITCH command

**MappingMask:** The mask transmitted by the previous DOWNLOAD\_SUM\_SCALING\_DATA command.

**pos2high\_th:** The lowest numbered address having a memory contents of 01. (Reference Figure 3-5.) This verifies that the LTA properly interpreted the DOWNLOAD\_SUM\_SCALING\_DATA command from the CCC.

**-pos2high\_th:** The lowest numbered address having a memory contents of 11. (Reference Figure 3-5.) This verifies that the LTA properly interpreted the DOWNLOAD\_SUM\_SCALING\_DATA command from the CCC.

**Scale\_err:** This byte has value 0x01 if there are transitions in the sum scaling table except at -pos2high\_th, pos2high\_th and between 0x7F and 00. (Reference Figure 3-5.) This verifies that the LTA properly interpreted the DOWNLOAD\_SUM\_SCALING\_DATA command from the CCC.

After this command is executed, all status words are set to zero. This allows the CCC to tell whether commands are being sent as expected.

Interface Control Document Between ALMA Phasing Project And ALMA Computing Doc #: ALMA- 05.11.00.00-70.35.25.00-A-ICD Date: 2014-10-07 Status: Draft (Draft, Pending, Approved, Released, Superseded, Obsolete) Page: 22 of 44

#### 3.2.2.2 Protocols Specific to PIC Nodes

Eight copies of a new card, the PIC, must be added to the correlator to provide a phasing interface. Two cards are added to each quadrant, one for each polarization. The primary function of the card is to format the sum data, received from the correlator cards, into a VLBI-standard VDIF format. A short summary of the new protocols required includes:

- A protocol to *download* required header information for the VDIF data frames

- A protocol to *apply* the above header information

- A protocol to monitor the time and status in the PIC card

- A pair of protocols to initiate and monitor a test for data quality into the PIC

- A protocol to monitor the sum-data statistics

- A protocol to control the PIC card (power on/off, etc.)

Interface Control Document Between ALMA Phasing Project And ALMA Computing Doc #: ALMA- 05.11.00.00-70.35.25.00-A-ICD Date: 2014-10-07 Status: Draft (*Draft, Pending, Approved, Released, Superseded, Obsolete*) Page: 23 of 44

#### 3.2.2.2.1 DOWNLOAD\_VDIF\_HEADER

Type:Broadcast, Data\_msg\_ID = 8, Func code 2, type 0Description:Used to download header for VDIF frameTypical Interval:Before the start of data takingData in Data Messages:40 bytes

| Message<br>Payload | Broadcast Setup<br>Message on Control | Header Message on<br>Data Channel | Data<br>Msg 0 | Data<br>Msg 1 |      | Data<br>Msg 4 |

|--------------------|---------------------------------------|-----------------------------------|---------------|---------------|------|---------------|

| Bytes              | Channel                               |                                   | Msg ID 8      | Msg ID 8      | •••• | Msg ID 9      |

|                    | Transmit using<br>Message ID 5        | Transmit using<br>Message ID 8    |               |               |      |               |

| Data[0] | Data_msg_ID = 8     | Func_code=2            | PSN<br>(LSB) | Word 0<br>(LSB) | Word 6 (LSB) |

|---------|---------------------|------------------------|--------------|-----------------|--------------|

| Data[1] | 0 (spare)           | Struct_type = 0        | PSN          | Word 0          | Word 6       |

| Data[2] | Target mask 7 - 0   | LS struct size (bytes) | PSN          | Word 0          | Word 6       |

| Data[3] | Target mask 15 - 8  | MS struct size (bytes) | PSN          | Word 0          | Word 6       |

| Data[4] | Target mask 23 - 16 | 0 ("block nr 0") *     | PSN          | Word 1          | Word 7 (LSB) |

|         |                     |                        |              | (LSB)           |              |

| Data[5] | Target mask 31 - 24 | 0 (not used)           | PSN          | Word 1          | Word 7       |

| Data[6] | Target mask 39 - 32 | eVLBI = 1              | PSN          | Word 1          | Word 7       |

| Data[7] | Target mask 47 - 40 | 0 (not used)           | PSN          | Word 1          | Word 7 (MSB) |

|         |                     |                        | (MSB)        | (MSB)           |              |

From the start of transmission by the CCC, it takes less than 4 msec for the transmitted data to be downloaded into hardware.

In the VLBI community a particular standard, VDIF, is followed for writing data (additional info may be found below and in [RD 05]). APP shall follow this standard. Additionally it shall prepend a Packet Serial Number (PSN) to each packet to enable eVLBI. Each Phasing Interface Card (PIC) will produce a stream of VLBI Data Interchange Format (VDIF) packets. The rules governing the packet stream are rather complex in general. (See [RD 05] for all the details if you like.)

For the ALMA case, each PIC receives 2-bit data samples from each of the 32 62.5 MHz slices of the 2 GHz IF from its quadrant of the correlator. With a factor of 2 for Nyquist sampling, each PIC data stream thus produces

2bits/channel x 32 channels/sample x 2 x 62.5 Msamples/s

64 x 125 Mbits/second = 8000 Mb/s = 1000 MB/s =  $2^9 * 5^9$  B/s

The VDIF data packets must be a multiple of 8 B in length, and further, the data bits from each second must be parceled equally into an integral number of packets. Since these packets will be transmitted on a physical ethernet layer, that protocol imposes an additional limit of no more than 9000 B/packet (including the VDIF header and UDP packet overhead). The CASPER Roach design for the Ethernet implementation further restricts the VDIF portion to 8192.

Subject to these restrictions, the largest packet possible is 8000 B for a data rate of

(1000 MB/s) / (8000 B/packet) = 125000 packets/s

The Packet Serial Number is exactly 8 B that precede the VDIF header. The VDIF header is exactly 32 bytes that precede the data. These fields and data portion are shown schematically in a cartoon of a complete packet as shown in Figure 3-6.

In forming VDIF frames for the APP, the values received from the CAN protocol are used as follows:

| PSN                  | Used for the PSN of the first transmitted frame. In subsequent frames, the PSN increases by 1 per frame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Word 0, bits 0 to 29 | Used to set the initial value of time in the timing generator (in the ROACH FPGA) at the rising edge of the TE tic following the APPLY_VDIF_HEADER command. After this, the time increments based on the 125 MHz correlator clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Word 0, bits 30      | Always zero in all frames.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Word 0, bits 31      | Sets the initial value for this bit in the VDIF frame. The value of this bit can later be changed via a bit in the CAN command SET_PIC_CONTROL. It can also be changed to set to 1 if the hardware detects a problem that corrupts the data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| All "brown" bits     | All bits shaded with the color brown in Figure 3-6 are identical to the corresponding bits in the CAN message, for all frames. These are the same for all observations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| All "pink" bits      | All bits shaded with the color pink in Figure 3-6 are identical to the corresponding bits in the CAN message, for all frames. These may be set (by the observer) as desired.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Word 4, bits0 to 23  | <ul> <li>A "magic/sync" identifier that in effect identifies 2<sup>24</sup> "subversions", of which we use 16 at ALMA</li> <li>1. For the ALMA PICs, the value will be 0xA5AE5X where the least significant nibble is constructed as follows: <ol> <li>bit 0: 0 = X-pol PIC, 1 = Y-pol PIC</li> <li>bits 1 and 2: ALMA BL quadrant number minus 1 (i.e. the quadrants are named 1 through 4, so these bits will contain 0 through 3).</li> <li>bit 3: 1 = BL Correlator 0 = 2-ant correlator</li> </ol> </li> <li>2. For Mark6 testing, the format is not finalized. However, it currently encodes the nominal packet rate and information about test marks made in the data stream.</li> <li>3. For use in other applications, 0x000000 through 0x7FFFFF are available.</li> </ul> |  |  |  |  |

Interface Control Document Between ALMA Phasing Project And ALMA Computing Doc #: ALMA- 05.11.00.00-70.35.25.00-A-ICD Date: 2014-10-07 Status: Draft (*Draft, Pending, Approved, Released, Superseded, Obsolete*) Page: 25 of 44

Word 5 Words 6 and 7

A repeating series of eight 32-bit words is provided in Word 5 as shown in Table 3 These words will provide the value for the packet serial number of the first transmitted frame. Subsequent frames will increment this count by 1 per frame. Normally the recorder does not record the PSN that precedes the VDIF packet proper.

Interface Control Document Between ALMA Phasing Project And ALMA Computing Doc #: ALMA- 05.11.00.00-70.35.25.00-A-ICD Date: 2014-10-07 Status: Draft (*Draft, Pending, Approved, Released, Superseded, Obsolete*) Page: 26 of 44

|                   | 31                           | By                                          | te 3 | 24    | 23  | Byt                          | te 2   | 16         | 15     | By     | te 1       | 8        | 7           | Byt  | te O | 0           |

|-------------------|------------------------------|---------------------------------------------|------|-------|-----|------------------------------|--------|------------|--------|--------|------------|----------|-------------|------|------|-------------|

| PSN               |                              |                                             |      |       |     | [F                           | acket  | Serial     | Numb   | er LSV | V ]        |          |             |      |      |             |

| FSN               | [ Packet Serial Number MSW ] |                                             |      |       |     |                              |        |            |        |        |            |          |             |      |      |             |

| Word 0            | 0/1 0                        |                                             |      |       |     | Seconds from Reference Epoch |        |            |        |        |            |          |             |      |      |             |

| Word 1            | 0 0 Reference Epoch          |                                             |      | poch  |     | Data Frame # within second   |        |            |        |        |            |          |             |      |      |             |

| Word 2            | 0 0 0 n_chan_log2            |                                             |      | _log2 |     |                              | 0      | ata Fr     | ame Lo | ength  | (octets    | s: 629 c | or 1004     | l)   |      |             |

| Word 3            | 0 0                          | 0 0                                         | 0 1  |       | т   | hread I                      | D      |            |        |        |            | Stati    | on ID       |      |      |             |

| Word 4            | [                            | [ EDV = 0x02 ] [ Magic/Sync Word 0xA5AE5X ] |      |       |     |                              |        |            |        |        |            |          |             |      |      |             |

| Word 5            |                              | [ PIC Status Word ]                         |      |       |     |                              |        |            |        |        |            |          |             |      |      |             |

| Word 6            |                              | [ Packet Serial Number LSW ]                |      |       |     |                              |        |            |        |        |            |          |             |      |      |             |

| Word 7            |                              |                                             |      |       |     | [F                           | acket  | Serial     | Numb   | er MSV | <b>v</b> ] |          |             |      |      |             |

| Octet 0           | c15                          | c14                                         | c13  | c12   | c11 | c10                          | c09    | c08        | c07    | c06    | c05        | c04      | c03         | c02  | c01  | c00         |

|                   | c31                          | c30                                         | c29  | c28   | c27 | c26                          | c25    | c24        | c23    | c22    | c21        | c20      | c19         | c18  | c17  | c16         |

|                   |                              |                                             |      |       |     |                              | Octets | s 1 thro   | ough N | I_2    |            |          |             |      |      |             |

|                   |                              |                                             |      |       |     |                              |        |            |        |        |            |          |             |      |      |             |

| Octet N-1         | c15                          | c14                                         | c13  | c12   | c11 | c10                          | c09    | c08        | c07    | c06    | c05        | c04      | c03         | c02  | c01  | c00         |

|                   | c31                          | c30                                         | c29  | c28   | c27 | c26                          | c25    | c24        | c23    | c22    | c21        | c20      | c19         | c18  | c17  | c16         |

|                   |                              |                                             | -10  |       |     | -10                          | - 00   | -00        | -07    | -06    | - 05       | -04      | -00         | - 00 | - 04 | -00         |

| Octet<br>for 16ch | c15                          | c14                                         | c13  | c12   | c11 | c10                          | c09    | c08        | c07    | c06    | c05        | c04      | c03         | c02  | c01  | c00         |

|                   | c15                          | c14                                         | c13  | c12   | c11 | c10                          | c09    | c08        | c07    | c06    | c05        | c04      | c03         | c02  | c01  | c00         |

|                   |                              |                                             |      |       |     |                              |        |            |        |        |            |          |             |      |      |             |

| Octet<br>for 8ch  | c07                          | c06                                         | c05  | c04   | c03 | c02                          | c01    | c00        | c07    | c06    | c05        | c04      | c03         | c02  | c01  | c00         |

|                   | c07                          | c06                                         | c05  | c04   | c03 | c02                          | c01    | <b>c00</b> | c07    | c06    | c05        | c04      | <b>c</b> 03 | c02  | c01  | <b>c</b> 00 |

Figure 3-6. VDIF frame format for the PIC.

Interface Control Document Between ALMA Phasing Project And ALMA Computing Doc #: ALMA- 05.11.00.00-70.35.25.00-A-ICD Date: 2014-10-07 Status: Draft (*Draft, Pending, Approved, Released, Superseded, Obsolete*) Page: 27 of 44

| Data Frame #<br>within second<br>(bits 2 to 0) | Status<br>Word # | Field<br>Definitions | Field<br>Description                                                     |

|------------------------------------------------|------------------|----------------------|--------------------------------------------------------------------------|

| 0x0                                            | 0                | Bit 0:               | Bad Packet when = 1                                                      |

|                                                |                  | Bit 1:               | TE Error when = 1                                                        |

|                                                |                  | Bit 2:               | 125 MHz MMCM lock error when = 1                                         |

|                                                |                  | Bit 3 3:             | FPGA over-temperature error when = 1                                     |

|                                                |                  | Bit 4:               | SEU Error when = 1                                                       |

|                                                |                  | Bit 5:               | Delay controller error when = 1                                          |

|                                                |                  | Bit 6:               | Data Kill Enable when $= 1$ (first 2 usec of data in frame $0 \ 0 = 0$ ) |

|                                                |                  | Bits 8 - 7:          | Data source                                                              |

|                                                |                  |                      | when $= 00 \Rightarrow$ normal data from summer                          |

|                                                |                  |                      | when $= 01 =>$ incrementing count from PIC counter                       |

|                                                |                  |                      | when $= 10 \Rightarrow$ pseudo-random data from PIC pseudo-random data   |

|                                                |                  |                      | generator                                                                |

|                                                |                  |                      | when $= 11 \Rightarrow$ always zero                                      |

|                                                |                  | others               | spare                                                                    |

|                                                |                  | Bits 31 – 24         | FPGA personality version number                                          |

| 0x1                                            | 1                | Bits 31 to 28:       | 0x1                                                                      |

|                                                |                  | Bits 27 to 0:        | GPS offset from PIC 1PPS                                                 |

| 0x2                                            | 2                | Bits 31 to 28:       | 0x2                                                                      |

|                                                |                  | Bits 27 to 0:        | Maser offset from PIC 1PPS                                               |

| 0x3                                            | 3                | Bits 31 to 28:       | 0x3                                                                      |

|                                                |                  | Bits 27 to 0:        | TE offset from PIC 1PPS (measured at seconds 0, 6, 12,)                  |

| 0x4                                            | 4                | Bits 31 to           | 0x3000                                                                   |

|                                                |                  | 16:                  |                                                                          |

|                                                |                  | Bits 15 to 6         | FPGA_temperature                                                         |

|                                                |                  |                      | $Temp(oC) = ((FPGA\_temperature) * 503.975/1024)-273.15$                 |

|                                                |                  | Bits 5 to 0:         | not meaningful                                                           |

| 0x7 to 0x5                                     | 7 to 5           | spare                | In the VDIF frame, these words have values of 0x0000_0007,               |

|                                                |                  |                      | 0x0000_0006 and 0x0000_0005 respectively                                 |

Table 3. Definition of status words delivered in Word 5 of the VDIF frame as a function of Data Frame Number within second, bits 2 to 0.

In some cases, fewer than 32 channels will need to be recorded. In these cases, the frame rate and/or length are adjusted to meet the VDIF requirements. Table 3-1, below, summarizes the frame rate and length for all APP cases.

Interface Control Document Between ALMA Phasing Project And ALMA Computing Doc #: ALMA- 05.11.00.00-70.35.25.00-A-ICD Date: 2014-10-07 Status: Draft (*Draft, Pending, Approved, Released, Superseded, Obsolete*) Page: 28 of 44

| Number of IF Channels/frame | Frame Length (octets) |        |      | Real Time/frame  | Frames/sec |

|-----------------------------|-----------------------|--------|------|------------------|------------|

|                             | Serial Num            | Header | Data | (micro-se conds) |            |

| 32                          | 1                     | 4      | 1000 | 8                | 125000.00  |

| 16                          | 1                     | 4      | 1000 | 16               | 62500.00   |

| 8                           | 1                     | 4      | 1000 | 32               | 31250.00   |

| 4                           | 1                     | 4      | 1000 | 64               | 15625.00   |

| 2                           | 1                     | 4      | 625  | 80               | 12500.00   |

| 1                           | 1                     | 4      | 625  | 160              | 6250.00    |

Table 3-4. Summary of the frame timing and contents as a function of the number of IF channels.

The C167 depends on the CCC to supply all bits of the header except

- The Data Frame # within second (the FPGA can supply this because we always start at a 1-second boundary where this field must be zero

- The least significant nibble of the Magic Alignment word (see entry for Word 4 above)

- The Status Word

As a result, the CCC supplies the following (lsb on the left):

```

PSN[0] = {psn_lower - 32b}

PSN[1] = {psn_upper - 32b}

words[0] = {sec_from_ref_epoch (apply TE) - 30b}, {0 - 1b}, {0 (invalidity) - 1b}

words[1] = {0 - 24b}, {ref_epoch (semester since 2000) - 6b}, {0 - 2b}

words[2] = {frame_bytes (1004 or 629) - 24b}, {n_chan_log2 - 5b}, {0 - 3b}

words[3] = {station_id - 16b}, {thread_id - 10b}, {1 - 1b}, {0 - 5b}

words[4] = {0xA5EA50 (upper magic word) - 24b}, {0x02 (EDV) - 8b}

words[5] = {0 - 32b}

words[6] = {psn_lower - 32b}

words[7] = {psn_upper - 32b}

```