# DBBC3 Testing for APEX and Pico Veleta

Alan Roy

Sven Dornbusch

Gino Tuccari

Jan Wagner

Helge Rottmann

Lena Schürmann

MPIfR / Istituto di Radioastronomia

# DBBC3 EHT Design Review History

#### **2018 Aug+Sep:**

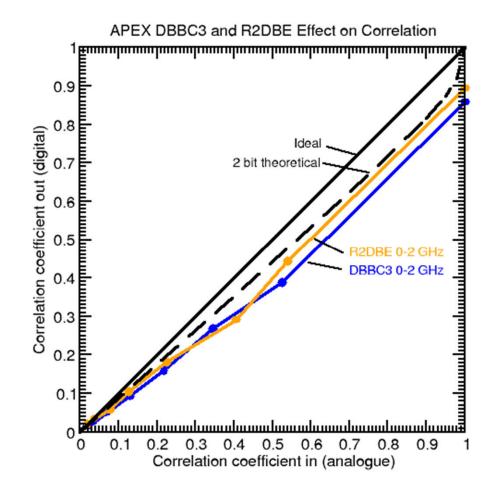

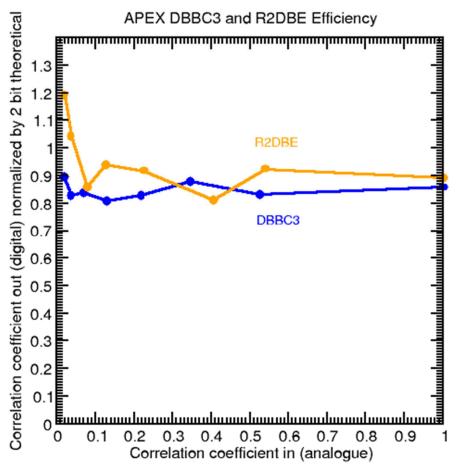

Tests on APEX DBBC3 in lab in Bonn System characterization, zero-baseline test, comparison to R2DBE, etc

#### **2018 Sep 13 Engineering Review Telecon**

J Weintroub (chair) et al. Generated 45 ORA's (Observation, Response & Action)

#### 2018 Sep 14-24

39 ORA's addressed, 6 ORA's remain open (primarily improve the efficiency measurement) Designed improved analogue noise source combiner network / ordered components

2018 Sep 25-Oct 24 (No activity - EHT 345 GHz fringe test, Alan in APEX)

**2018 Oct 25-Nov 5** Components arrive, assembled improved combiner network

Addressing ORA #27 (excess PN in 2048 MHz sampler clock)

Addressing ORA #21 (better efficiency measurement)

2018 Nov 6 This meeting (EHT Collaboration Meeting Nijmegen)

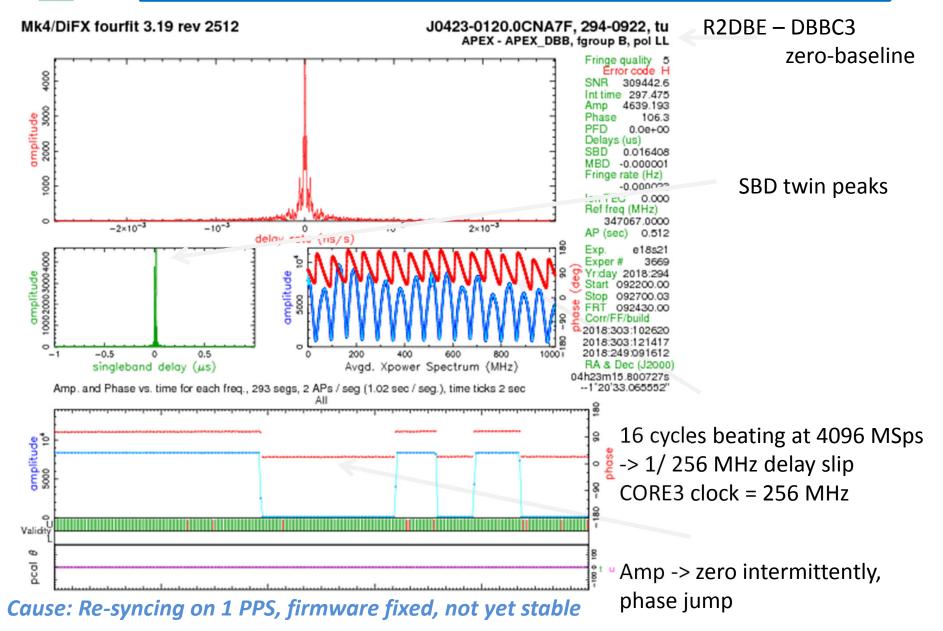

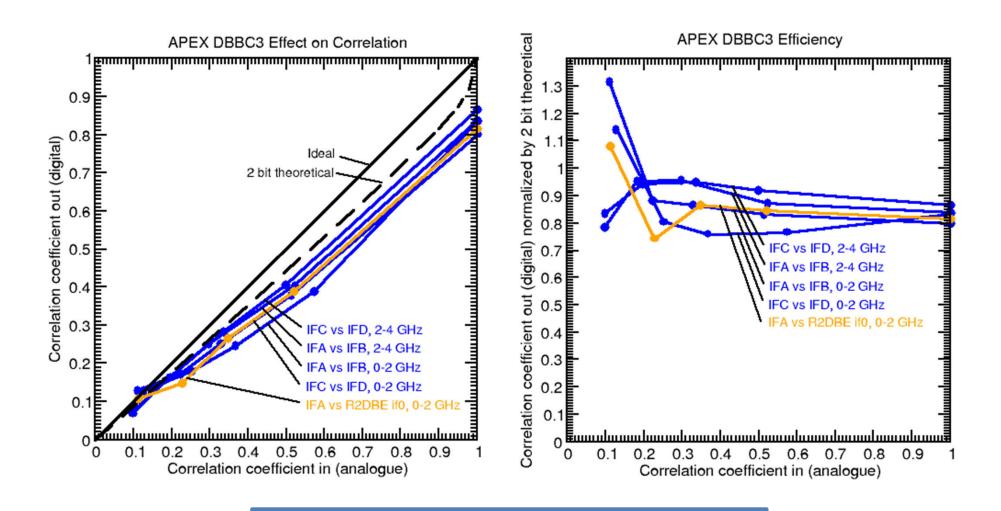

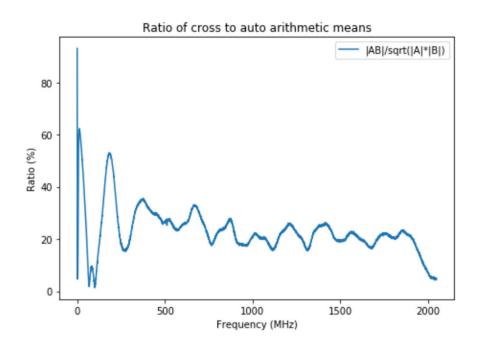

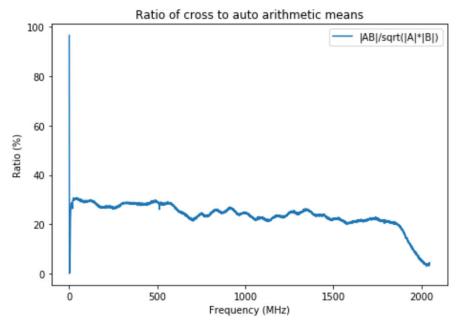

### **Zero Baseline Test:** zerocorr analysis example for $\rho_0$ = 0.336

Efficiency of each backend: 90 % to 93 %

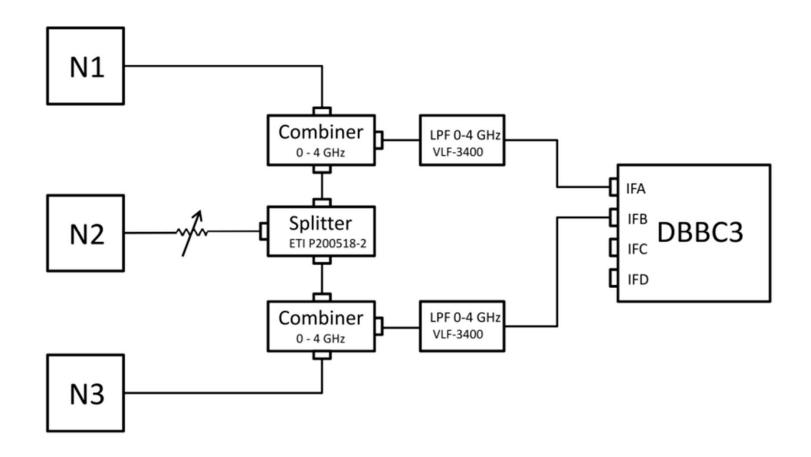

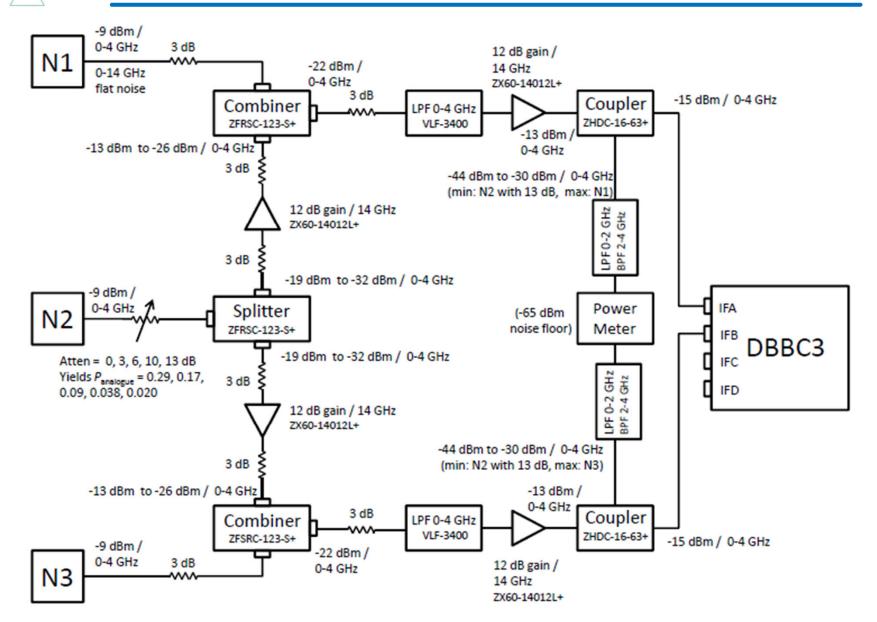

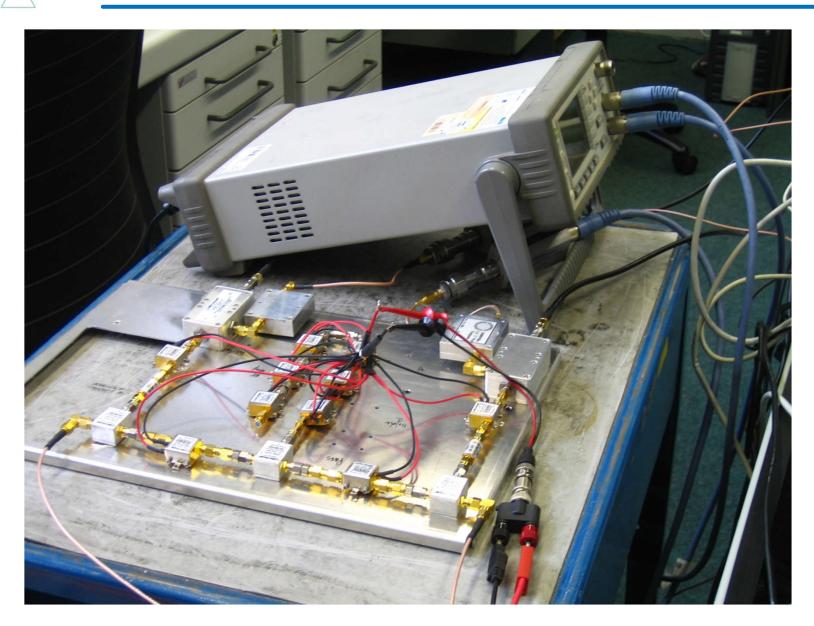

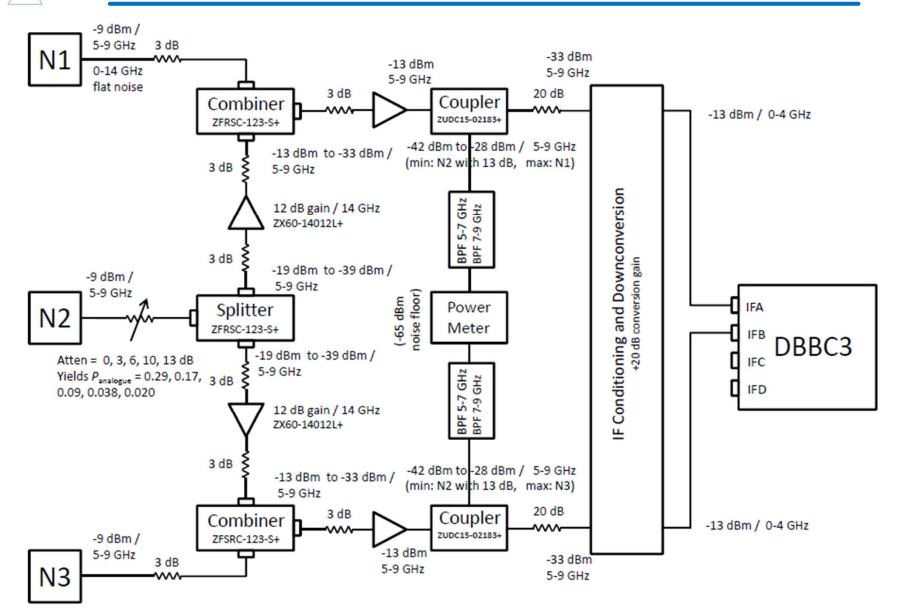

# Analogue Signal Preparation: 2018 Aug-Sep

### Analogue Signal Preparation: 2018 Oct-Nov

# Analogue Signal Preparation: 2018 Oct-Nov

#### Zero Baseline Test

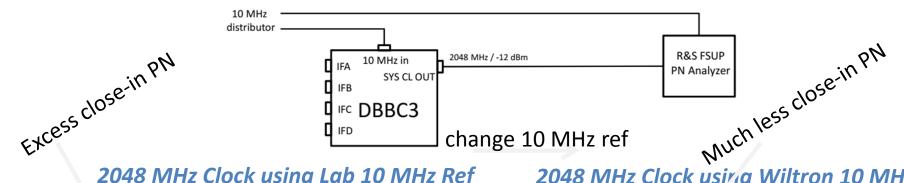

### ORA#27 Timing Stability: Sampler Clock

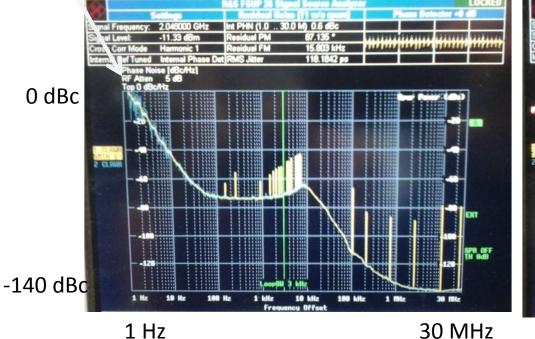

#### 2048 MHz Clock using Lab 10 MHz Ref

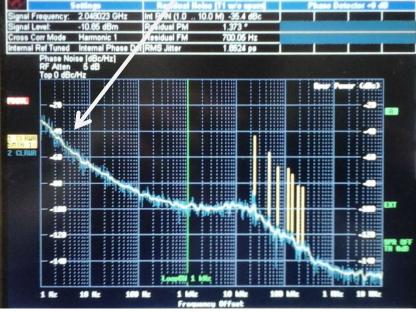

2048 MHz Clock using Wiltron 10 MHz Ref

1 Hz

87° RMS random phase jitter(!!!)

30 MHz

1.9° RMS random phase jitter

### Analogue Signal Preparation: 2018 Oct-Nov

# ORA#(35) Bandpass Ripple

• Improved component selection in analogue combiner

2018 Sep

2018 Nov 05

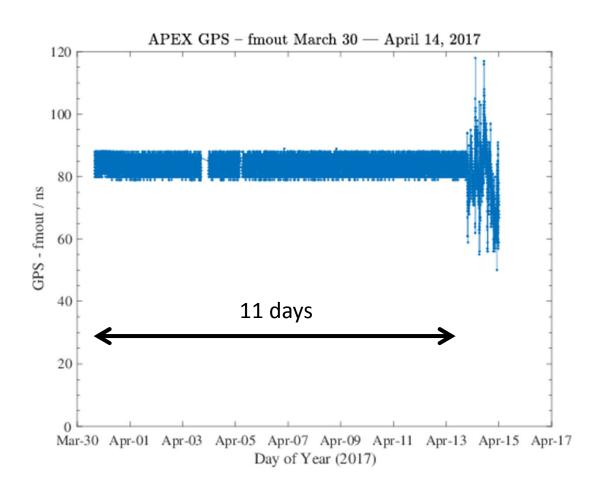

### ORA#1 Too-Stable 1 PPS GPS-FMOUT

- Cause: firmware performs re-sync each second on 1 PPS input

- Fix: 2-line change in firmware, recompilation not stable (Xilinx ISE issue; need PlanAhead)

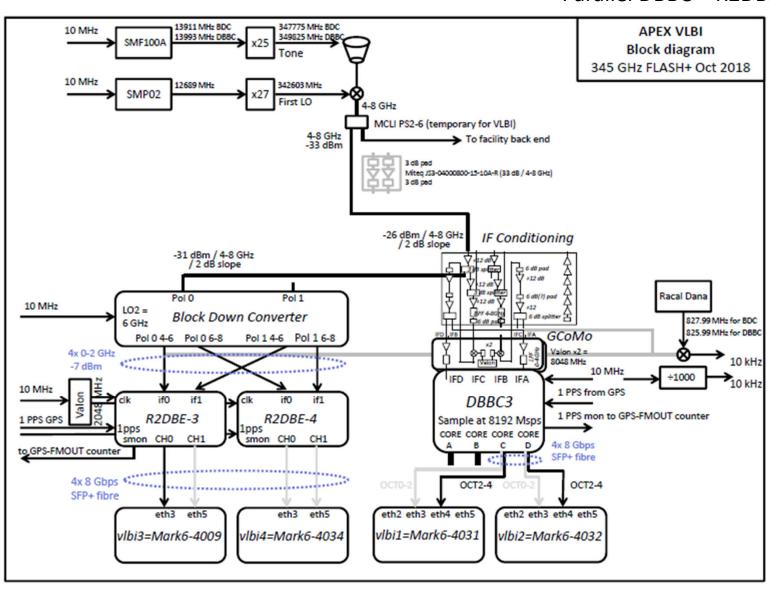

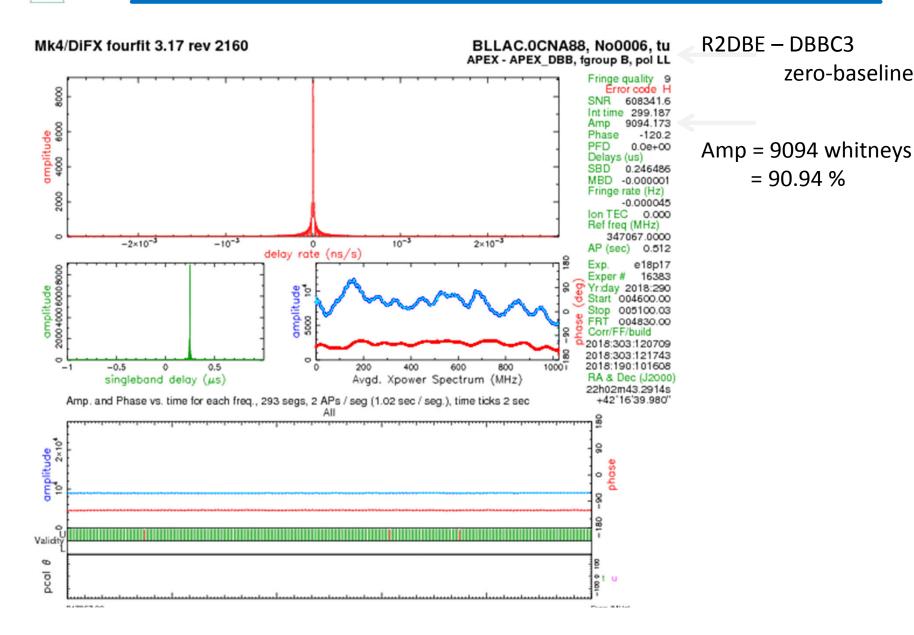

# On-Sky Fringe Test EHT Oct 345 GHz

#### Parallel DBBC + R2DBE

# On-Sky Fringe Test EHT Oct 345 GHz

# On-Sky Fringe Test EHT Oct 345 GHz