# DBBC3: next generation versatile VLBI backend

G. Tuccari<sup>1,2</sup>, W. Alef<sup>2</sup>, M. Wunderlich<sup>2</sup>, S. Buttaccio<sup>1</sup>, D.A. Graham<sup>2</sup>, H. Rottmann<sup>2</sup>, A. Bertarini<sup>2</sup>, A. Roy<sup>2</sup>, S. Dornbusch<sup>2</sup>, A. Felke<sup>2</sup>

1 INAF Istituto di Radioastronomia, Sezione di Noto, Contrada Renna, 96017 NOTO (SR), ITALY 2 Max Planck Institute for Radio Astronomy, Auf dem Hügel 69, 53121 BONN, GERMANY

### **DBBC3: Introduction**

**DBBC3** has been developed with support by RadioNet3 in the Joint Research Activity **DIVA**

**DBBC3** is the next generation digital backend for VLBI and other applications

**DBBC3** is fully backwards **compatible with the DBBC2**, the most widely adopted VLBI backend

**DBBC3** is a versatile backend, as it can serve the needs of the **EVN**, **EHT**, and **geodesy**

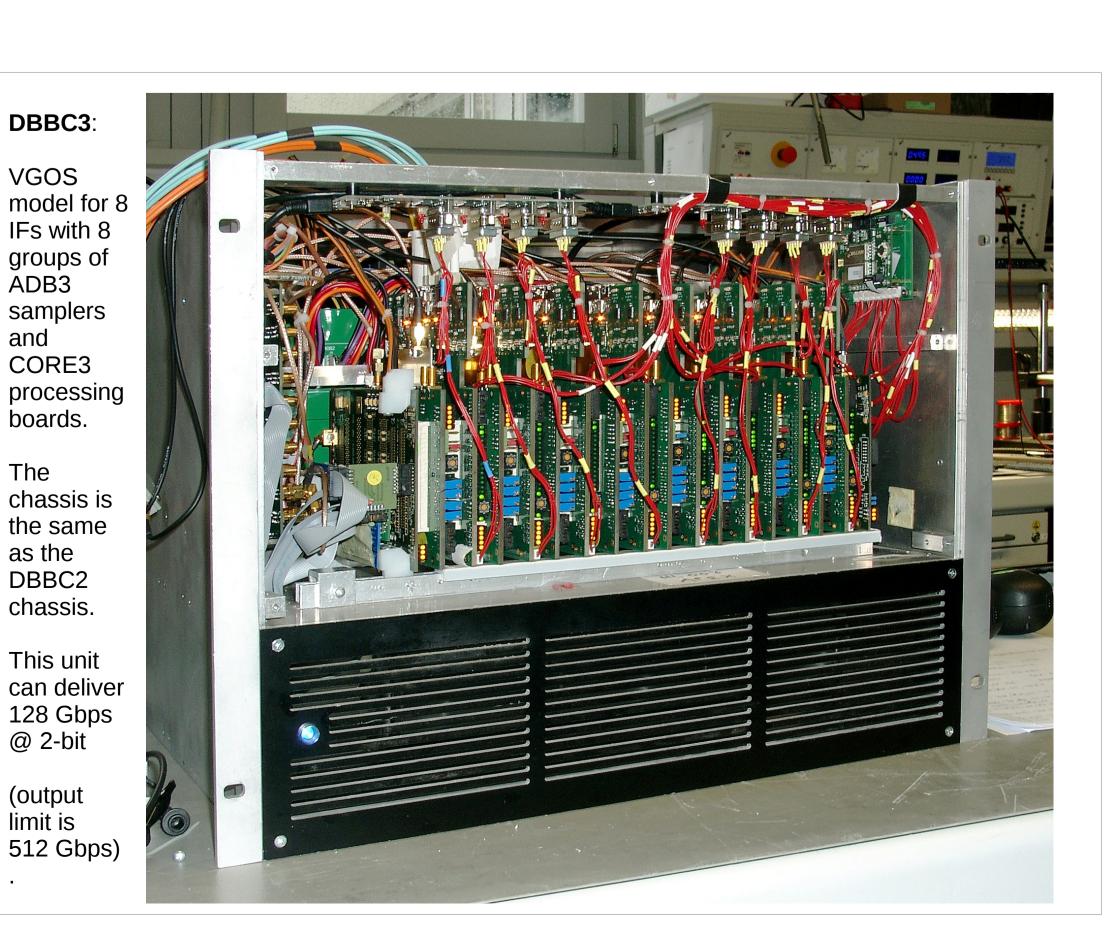

DBBC3 offers from 1 IFs to 8 IFs on input with 16 Gbps to 128 Gbps on output (2-bit samples)

**DBBC3** is a cost-effective backend which out-competes other less flexible solutions

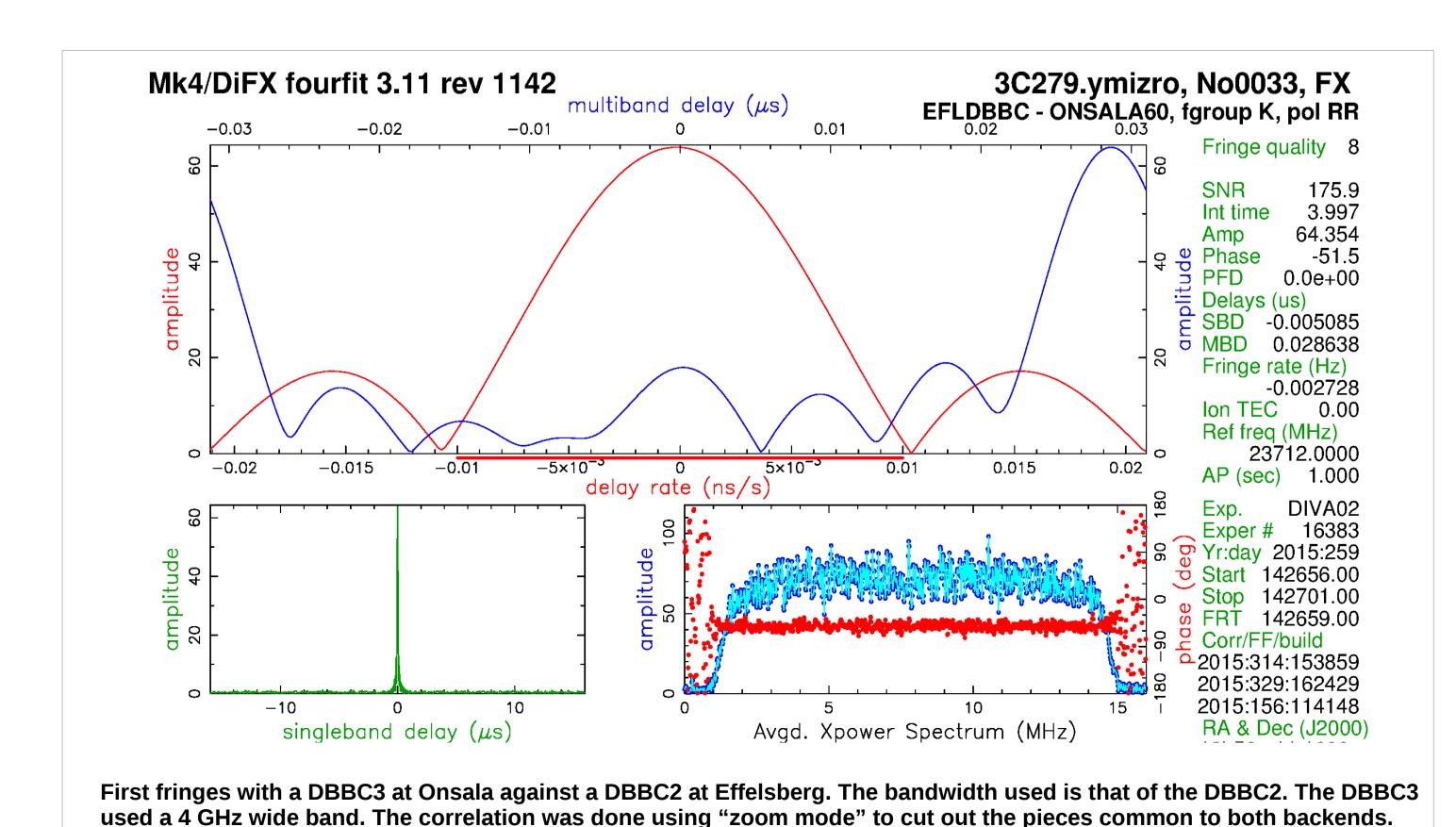

DBBC3 Status: in production; fringes Hobart-Ishioka & Onsala-Effelsberg; DBBC2 firmware porting ongoing

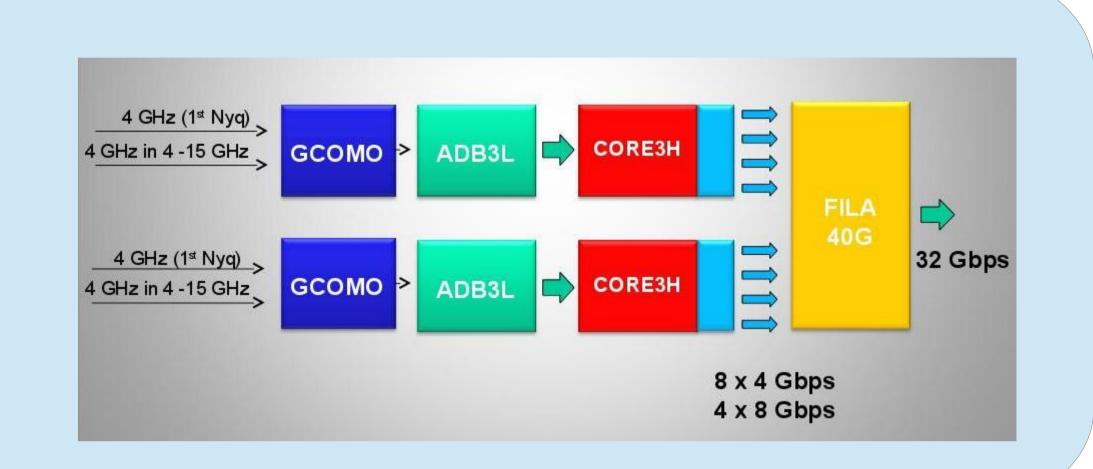

#### **DBBC3** components

- **GCOMO:** analogue conditioning: 0-4 GHz direct and and down-converter for pre-filtered 4 GHz portion in the range 4 GHz 15 GHz

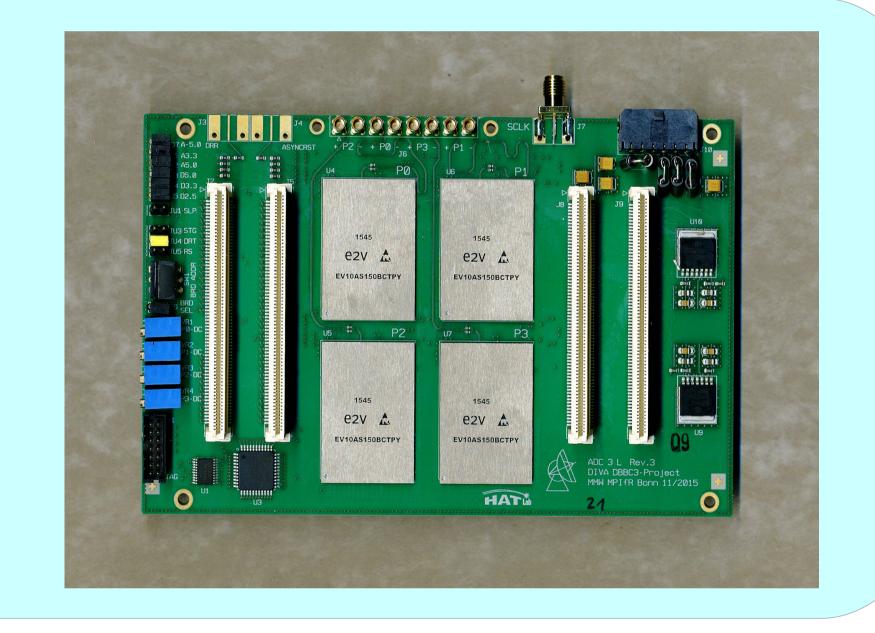

- ADB3 sampler board: sampling w. interleaved 4 samplers

- CORE3 processing unit: single FPGA board with up to 8x 10 Gb Ethernet output

- FIIA40G post-processing & recording unit (optional; developed by Onsala Observatory)

- DBBC chassis (compatible with DBBC2)

- Ancillary boards: computer, GCAT (GHz Clock And Timing), PHA (Phase adapter for the ADB3 board; GPS distribution etc.

## **ADB3 Sampler specifications and architecture**

- 4 samplers: 1x 4 GHz, 2x 2GHz, 4x 1GHz

- Interleaved sampling with novel automatic calibration routine

- Number of IFs: 1 2 4

- Equivalent sample rate ea. IF: 8 GSps

- Instantaneous bandwidth ea. IF: 4 GHz

- Sampling representation: 10 bit

- Real/complex sampling

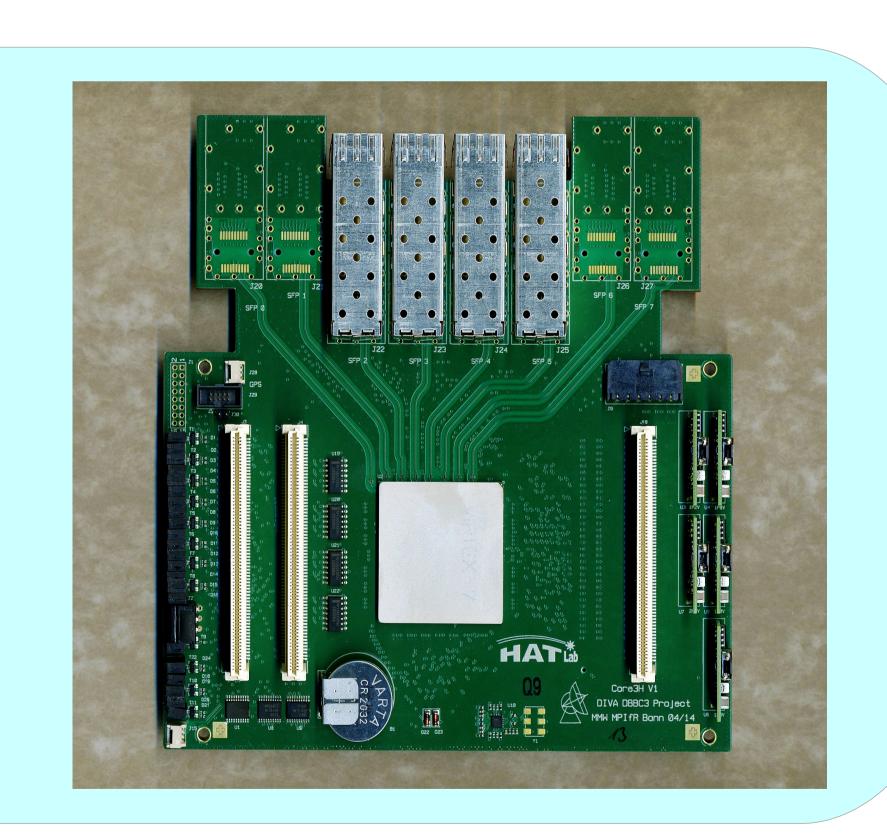

# **CORE3** processing unit

- Number of inputs: max 48 serial links 11.2 Gbps

- Number of Outputs: max 8 serial links 10 Gbps Ethernet

- Input sampling representation: 8-10 bit

- Processing capability: max 5 TMACS (multiplication-accumulation per second)

- Output: VDIF Ethernet packets, ≥ 32 Gbps

- Pass-band filtering with 100 dB out of band suppression possible

- Processing capability: wide-band DDC, wide-band PFB, DCS

- VLBI modes:

- Direct sampling conversion: 4 GHz / 1 GHz

- Polyphase filterbanks: 256 MHz 64 MHz 32 MHz

- Digital downconverters: 128 MHz 64 MHz 32 MHz 16 MHz 8 MHz 4 MHz 2 MHz

- 16 down-converters possible for bandwidths ≤ 16 MHz